The US company MicroWay (also known for their NDP compiler range), presented an i860 ISA card called NumberSmasher 860.

It was available in two speed grades, costing 11698 DM (@33 MHz) or 14170 DM (@40 MHz). The needed compiler (C, Pascal or Fortran) was an 3135 DM extra.

This 16-bit ISA card featured an 40MHz i860, 4 or 8MB of ram and one INMOS OS-link controlled by a IMSC012 on a litte PCB, hiding 2 additional IMSC012 below it on the main PCB.

It is possible to connect one IMS C012 to to the ISA host bus to “feed” the Number Smasher 860 with programs and data (seedocumentation at the bottom of this page).

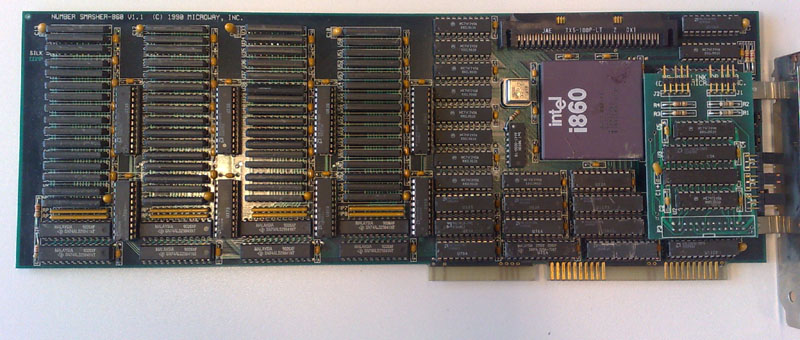

Here’s the board in its full beauty:

The left half is occupied by the 8MB RAM. The right half is all bus-logic, buffers and drivers. At the top is a very custom HD-connector – thanks to Jörg Heilmann I now know that this is the FiFo-Connector counting 100 pins. Again thanks to Jörg I also have4 pages of documentation to this connector which was designed to connect the FIFO I/O board (available as ISA and EISA version) to.

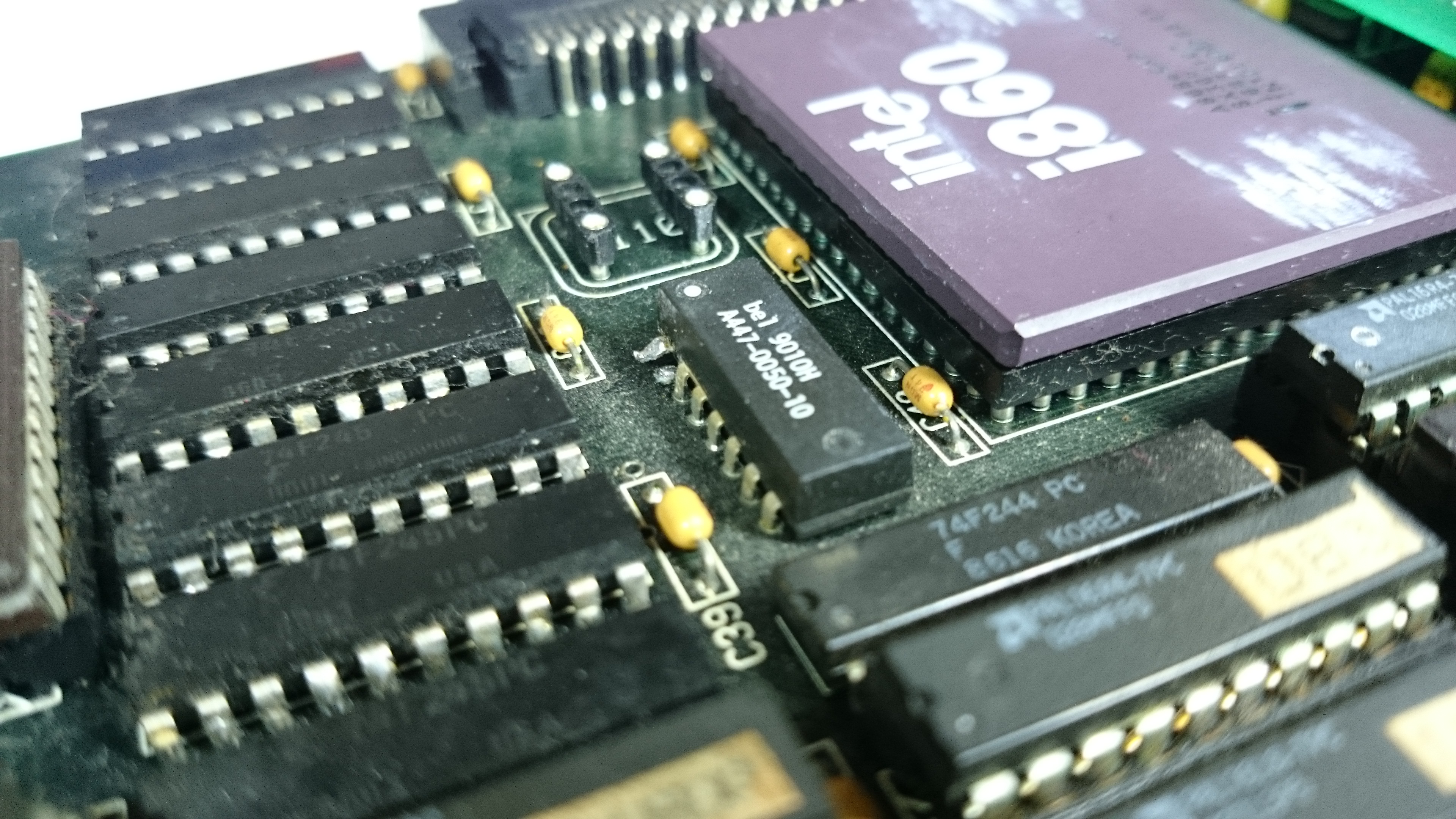

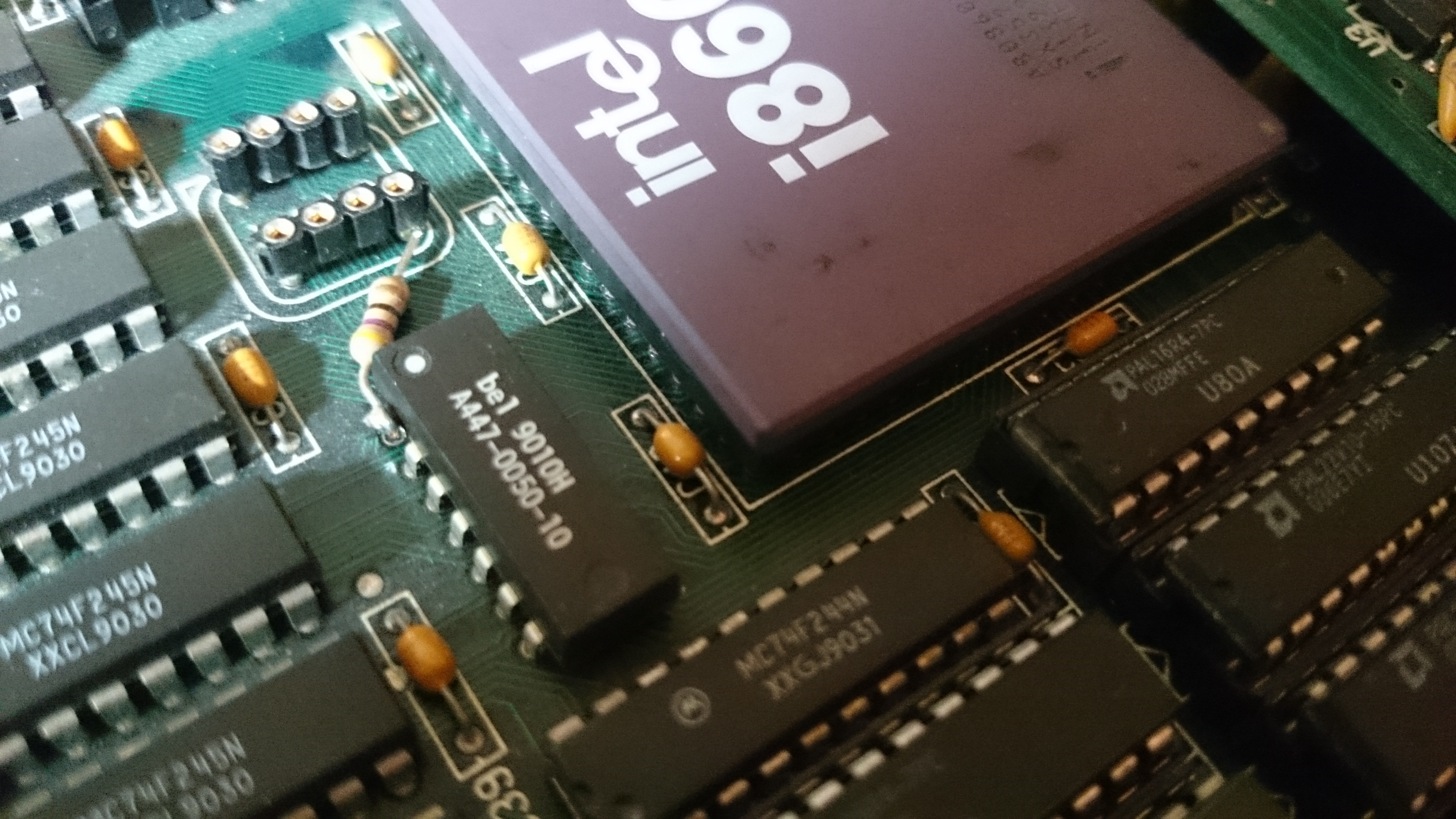

On a little separate PCB (having “LINK DR V2.0” printed on it) connected to P3 some sort of additional communication part was placed, consisting of an octal transceiver, one INMOS C012 link-adapter a PAL and an octal buffer featuring two 4-pin connectors (J1 & J2).

- J1 – GND – GND(code) – to pin 3 of J4 – to pin 3 of J3 – GND

- J2 – GND – GND(code) – to pin 16 of P3 – to pin 14 of P3 – GND

Additionally there are 3 configuration jumpers – function as far as my measurements go:

- J3 – Connects pin 18 of the board-connector (LinkIn lower onboard C012) to either LinkOut of the C012 (jumper on upper pin) or to the 4th pin of J1 (jumper on lower pin).

- J4 – Connects pin 20 of the board-connector (LinkOut lower onboard C012) to either LinkIn of the C012 (jumper on upper pin) or to the 3rd pin of J1 (jumper on lower pin).

- J5 – Linkspeed for the IMSC012 (upper is 20Mbps, lower is 10Mbps)

Documentation

As I have next to no official documentation about this board I would be very glad to hear from anybody who knows the tiniest bit about this card! AFAIK the original “manual” wasn’t bigger than 13 pages… pretty lame for a board costing as much as a small car back in those days.

Thanks to Jörg Heilmann, I got my first piece of original documentation: The 100 pin FIFO-Connector is described on these four pages. Not much but a start!

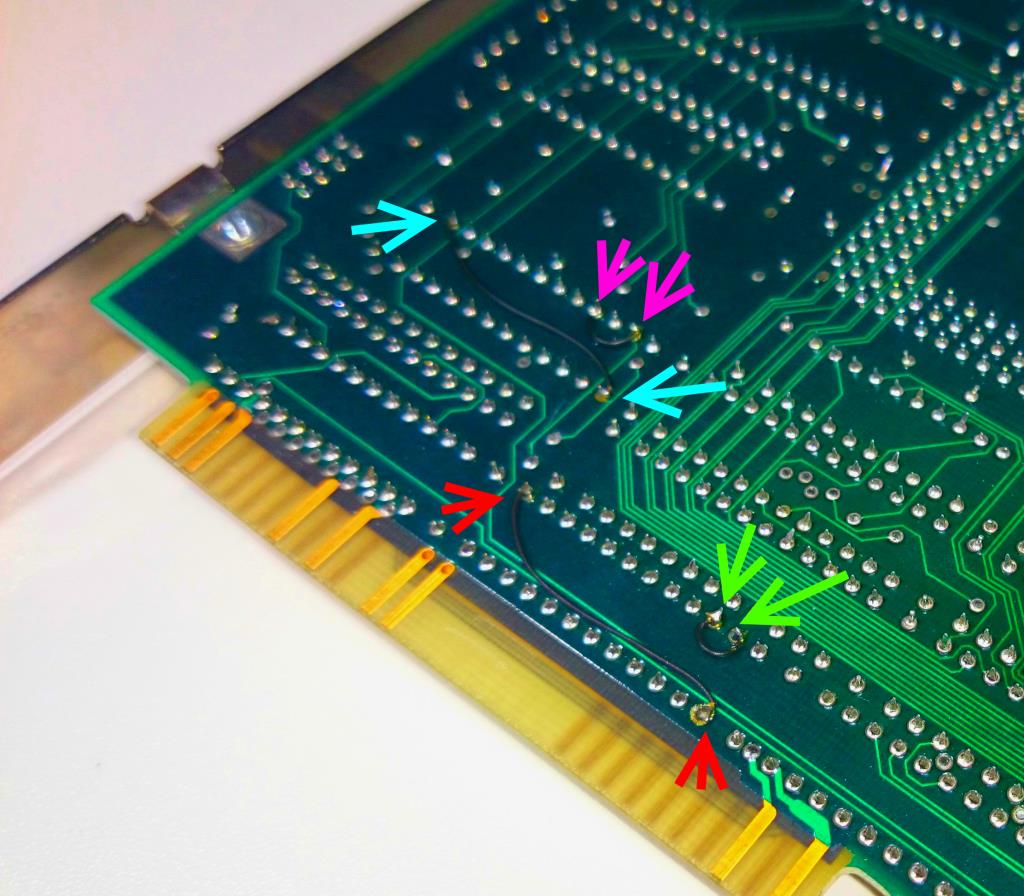

Here’s what I found out about the P3 connector on the board, having the “LINK DR” PCB plugged into it. If you have a look at the picture above, I’m start counting pins from bottom right continuing zig-zag like this:

26 oooo...oooo 2

25 oooo...oooo 1

1 – VCC

2 – CLK 5MHz

3 – Reset of the C012 (Pin 11) goes directly to the i860 reset-pin

4 – GND

5 – D7 from ISA Bus

6 – D6 from ISA Bus

7 – D5 from ISA Bus

8 – D4 from ISA Bus

9 – D3 from ISA Bus

10 – D2 from ISA Bus

11 – D1 from ISA Bus

12 – D0 from ISA Bus

13 – ???

14 – Pin 2 of the upper onboard C012

15 – ???

16 – Pin 1 of the upper onboard C012

17 – ISA Pin B8 (NoWS)

18 – Pin 2 of the lower onboard C012

19 – ???

20 – Pin 1 of the lower onboard C012

21 – MEMW to ISA

22 – MEMR to ISA

23 – ???

24 – ???

25 – VCC

26 – GND

From these findings I conclude that J2 is directly connected to the upper onboard C012 while J1 is either connected to the lower onboard C012 (J3 & 4 set to upper pins) or to the C012 on the LINK DR (J3 & 4 set to lower pins) which has its data-lines connected to the ISA bus.

On the main-card are 3 other jumpers:

- J1 & J2 – Set the connection speed of the two C012 on the card

- J3 – Select the ISA IRQ. Top down: IRQ 10, 11, 12, 15.

Everything else I have for now is a single article from the German computer magazine “c’t” (3/91,p.164 by O. Grau and A. Stiller) giving a bit more insight in the way the card works:

“Das Interface zum ISA-Bus des Hostrechners ist auf einer kleinen austauschbaren Platine untergebracht und basiert auf einem FIFO. Durch ihn geht sämtlicher I/O. Ein vergleichsweise aufwendiges Protokoll sorgt für einen recht langsamen Datentransfer, so besteht jeder Transfer aus dem Kennbyte 0 (Schreiben) oder 1 (Lesen), gefolgt von der Zieladresse (vier Bytes) und dem Datum (vier Bytes).”

The interface to the hosts ISA-bus is located on a small changeable board and is based on a FIFO [buffer]. All I/O is going through this. A comparably complex protocol is the reason for the data transfer being a bit slow. Each transfer consists of a ID-byte (0=write, 1=read) followed by the target address (four bytes) and the data (four bytes).

This “protocol” sounds very familiar to me. INMOS had the same, calling it PEEK and POKE… I’m still evaluating this, so stay tuned.

[11/05/10] Great News! I had some time and did some deeper investigation… hardware archaeology at its best 😉 So read on in the next post… it’s dissection time!